Digital Design

Advantages of Digital

Section titled “Advantages of Digital”- Reproducibility of results

- Ease of Design

- Flexibility

- Programmability

- Speed

Logic Levels

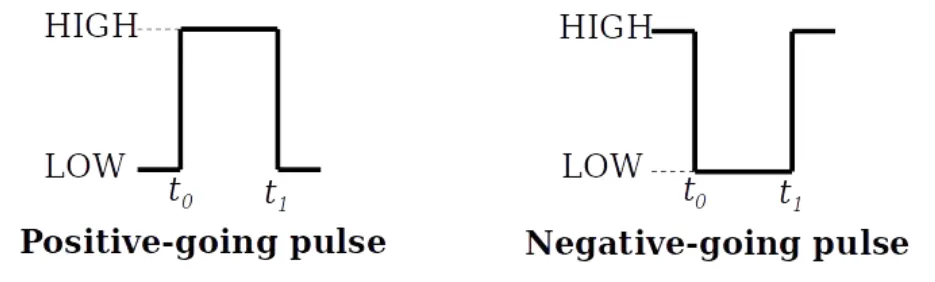

Section titled “Logic Levels”- Ideally : HIGH(1) and LOW(0)

- Practically : In CMOS

- HIGH: 2V - 3.3V

- LOW: 0V - 0.8V

Digital Waveforms

Section titled “Digital Waveforms”

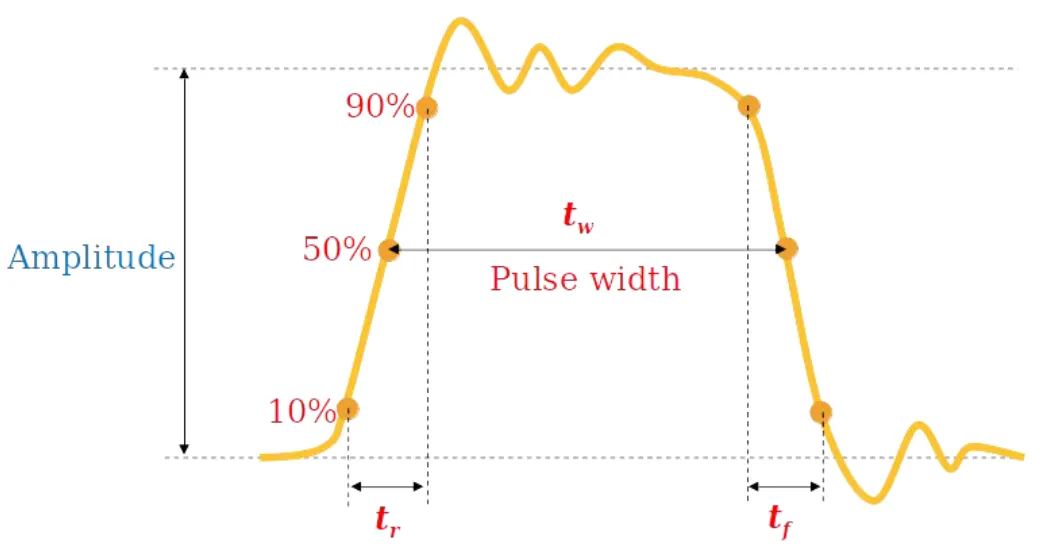

Non-ideal Pulse

Section titled “Non-ideal Pulse”

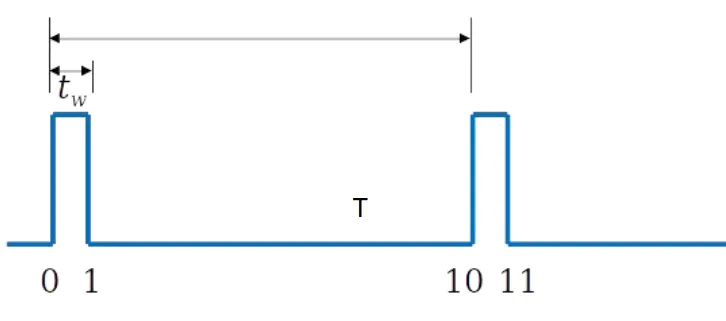

Duty Cycle

Section titled “Duty Cycle”

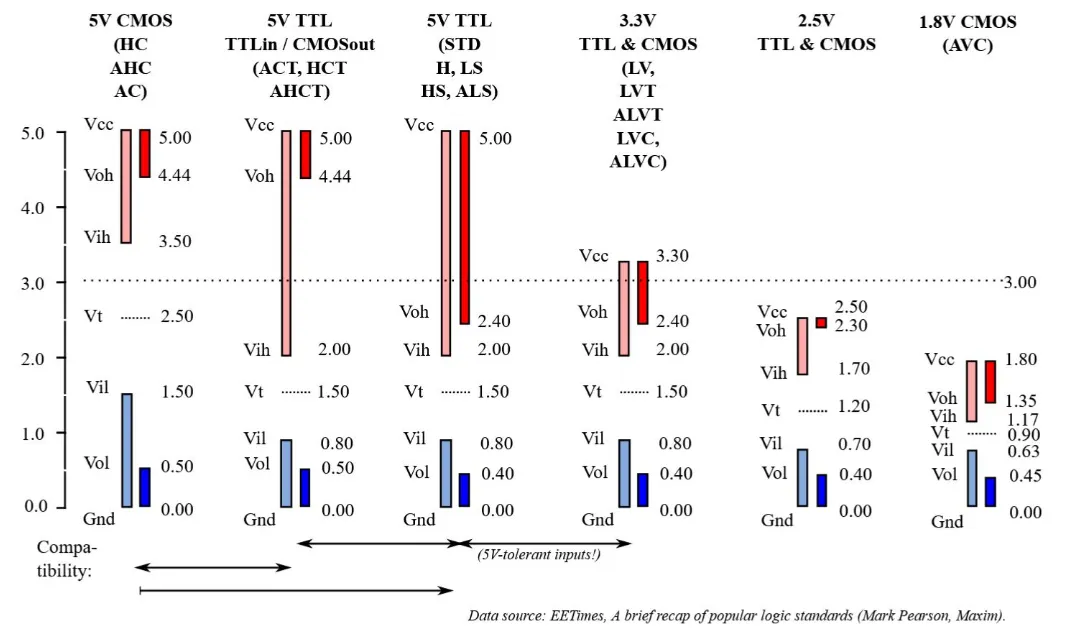

Digital Logic Families

Section titled “Digital Logic Families”Collection of different integrated circuit chips that have:

- Similar input, output and internal circuit characteristics

- Methods to implement all necessary logic functions

Chips from the same family can be interconnected to perform any desired logic function

Chips from different logic families may not be compatible

Electrical behavior of Logic Families

Section titled “Electrical behavior of Logic Families”- Logic Voltage level

- DC noise margins :

Highest

LOWvoltage of an output must be always lower than the highest voltage that an output can reliably interpret asLOW - Fanout : Number of inputs connected to a given output

- Speed

- Power Consumption

- Noise / Interference : Cosmic Rays

- Electrostatic discharge

Binary Data transfer

Section titled “Binary Data transfer”- Serial : Send one bit at a time

- Parallel : All bits in a group are sent out on separate lines at the same time

- Serial vs Parallel: Serial use less transmission lines Takes more time to transfer